### ■ 产品描述

FS6224 是一款高性能原边控制器,可提供高精度恒压和恒流输出性能,尤其适合于小功率离线式充电器应用中。

在恒压输出模式中,FS6224 采用多模式工作方式,即调幅控制(AM)和调频控制(FM)相结合,提高了系统的效率和可靠性。在恒流输出模式中,芯片采用调频控制方式,同时集成了线电压和负载电压的恒流补偿。采用(FS6224)可以工作无异音,同时可保证优异的动态性能。利用集成的线损补偿功能,可获得高性能的恒压输出表现。

FS6224 集成有多种保护功能: VDD 欠压保护 (UVLO)、VDD 过压保护 (OVP)、逐周期限流保护 (OCP)、短路保护 (SLP) 和 VDD 箝位等。

### ■ 应用领域

- 手机充电器

- AC/DC 适配器

- LED 照明驱动

- 典型功率推荐:

85-265Vac: 24W

## ■ 主要特点

- 集成 650V MOSFET

- ±4% 恒流、恒压精度

- 待机功耗<70mW

- 多模式原边控制方式

- 工作无异音

- 优化的动态响应

- 可调式线损补偿

- 集成线电压和负载电压的恒流补偿

- 集成完善的保护功能:

- ➤ 短路保护 (SLP)

- ▶ 过温保护(0TP)

- ▶ 逐周期限流保护 (0CP)

- ▶ 前沿消隐 (LEB)

- ▶ 管脚悬空保护

- ▶ VDD 过欠压保护和箝位保护

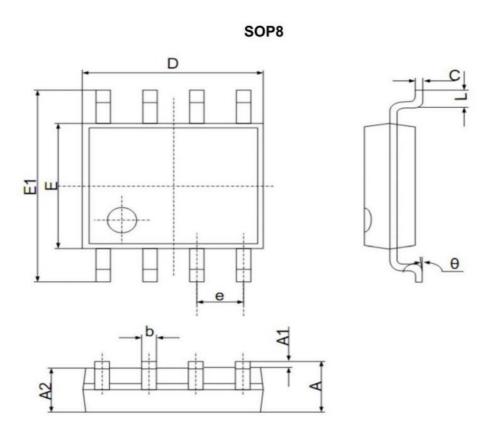

- 封装形式 SOP-8

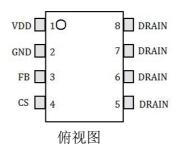

### ■ 管脚封装

## ■ 管脚功能描述

| 编号         | 名称    | 功能描述                                                     |

|------------|-------|----------------------------------------------------------|

| 1          | VDD   | 芯片供电脚。                                                   |

| 2          | GND   | 芯片参考地。                                                   |

| 3          | FB    | 系统反馈管脚。辅助绕组电压经电阻分压后送至 FB 管脚,用于 CV 模式输出电压控制及 CC 模式输出电流控制。 |

| 4          | CS    | 电流采样输入脚。                                                 |

| 5, 6, 7, 8 | DRAIN | 内置功率 MOSFET 漏极。                                          |

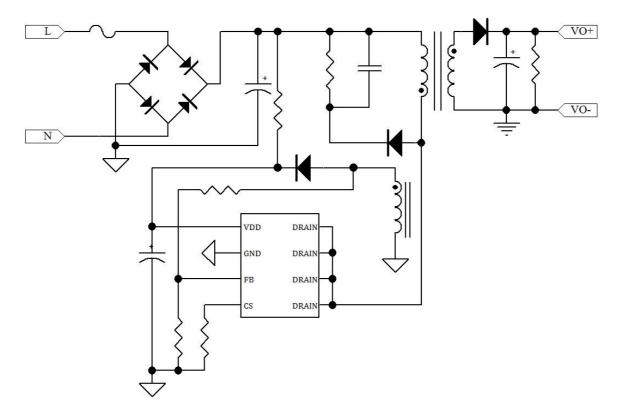

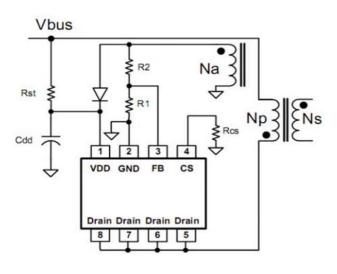

# ■ 典型应用电路

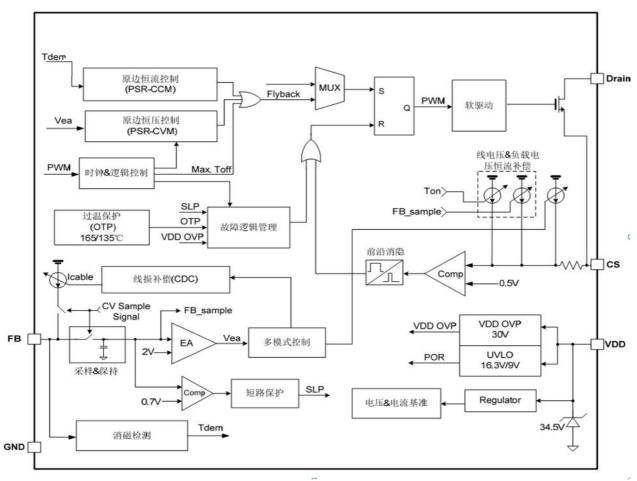

## ■ 内部框图

# ■ 极限参数(备注 1)

| 参数              | 数值          | 单位   |

|-----------------|-------------|------|

| DRAIN 电压        | -0.3 to 650 | ٧    |

| VDD 直流供电电压      | 34. 5       | ٧    |

| VDD 直流钳位电流      | 10          | mA   |

| CS 电压范围         | -0.3 to 7   | ٧    |

| FB 、SEL 电压范围    | -0.7 to 7   | ٧    |

| 封装热阻结到环境(SOP-8) | 165         | °C/W |

| 最大结温            | 175         | °C   |

| 储藏温度范围          | -65 to 150  | °C   |

| 焊接温度(焊接,10 s)   | 260         | °C   |

| ESD 人体模型        | 3           | kV   |

| ESD 机器模型        | 250         | ٧    |

## ■ 推荐工作条件(备注 2)

| 参数                 | 数值        | 单位  |

|--------------------|-----------|-----|

| VDD 供电电压           | 11 to 27  | V   |

| 工作环境温度             | -40 to 85 | °C  |

| 最高工作频率 @ 满载,反激原边控制 | 70        | kHz |

| 最低工作频率 @ 满载,反激原边控制 | 35        | kHz |

**■ 电气参数**(TA = 25°C, VDD=18V, 除非另有说明)

| 符号                               | 参数          | 测试条件           | 最小    | 典型    | 最大    | 单位  |

|----------------------------------|-------------|----------------|-------|-------|-------|-----|

| 供电部分(                            | VDD 管脚)     |                |       |       |       |     |

| I <sub>VDD_ST</sub>              | VDD 启动电流    |                |       | 2     | 15    | uA  |

| l <sub>VDD_OP</sub>              | VDD 工作电流    |                | 0. 3  | 0. 7  | 0. 9  | mA  |

| VDD_Standy                       | VDD 静态电流    |                |       | 0. 5  | 1     | mA  |

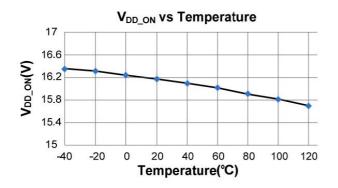

| $V_{\text{DD\_ON}}$              | VDD 开启电压    |                | 15    | 16. 3 | 17. 5 | ٧   |

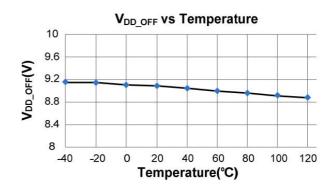

| $V_{\scriptscriptstyle DD\_OFF}$ | VDD 关断电压    |                | 8     | 9     | 10    | ٧   |

| $V_{\text{DD\_OVP}}$             | VDD OVP 阈值  |                | 28    | 30    | 32    | ٧   |

| $V_{\text{DD\_Clamp}}$           | VDD 钳位电压    | I (VDD )= 7 mA | 32. 5 | 34. 5 | 36. 5 | ٧   |

| <b>反馈控制部</b>                     | 分(FB 管脚)    |                |       |       |       |     |

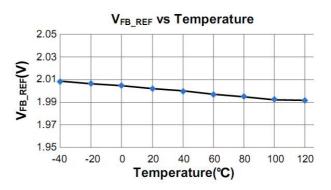

| VFBREF                           | 内部误差放大器参考基准 | È              | 1. 97 | 2. 0  | 2. 03 | V   |

| V <sub>FB_SLP</sub>              | 短路保护阈值      |                |       | 0. 7  |       | V   |

| TFB_Short                        | 短路保护去抖时间    | (备注 3)         |       | 10    |       | ms  |

| V <sub>FB_DEM</sub>              | 消磁比较器阈值     |                |       | 25    |       | mV  |

| Toff_min                         | 最短关断时间      | (备注 3)         |       | 2     |       | us  |

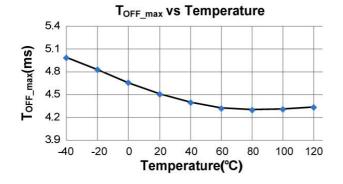

| Toff_max                         | 最长关断时间      |                |       | 5     |       | ms  |

| Cable_max                        | 最大线补电流      |                |       | 63    |       | uA  |

| <b>电流采样部</b>                     | 分 (CS 管脚)   | ,              | '     |       | 1     |     |

| TLEB                             | 前沿消隐        |                |       | 500   |       | ns  |

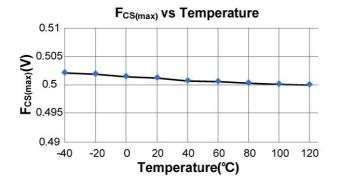

| Vcs (max)                        | 过流保护阈值      |                | 490   | 500   | 510   | mV  |

| T <sub>D_0C</sub>                | 过流保护关断延迟时间  |                |       | 100   |       | ns  |

| 5片过温保                            | 护           |                |       |       | •     |     |

| TsD                              | 关断温度        | (备注 3)         |       | 165   |       | ° C |

| Trc                              | 恢复温度        | (备注 3)         |       | 135   |       | °C  |

| 功率三极管部           | 分(DRAIN 管脚)      |        |     |       |   |

|------------------|------------------|--------|-----|-------|---|

| V <sub>DSS</sub> | 功率 MOSFET 漏源击穿电压 |        | 650 |       | ٧ |

| $R_{dson}$       | 静态漏源导通电阻         | FS6224 |     | 1. 25 | Ω |

**备注 1:** 超出列表中极限参数可能会对芯片造成永久性损坏。极限参数为额定应力值。在超出推荐的工作条件和应力的情况下,器件可能无法正常工作,所以不推荐让器件工作在这些条件下。过度暴露在高于推荐的最大工作条件下,会影响器件的可靠性。

备注 2: 超出上述工作条件不能保证芯片正常工作。

备注 3: 参数取决于设计, 批量生产制造时通过功能性测试。

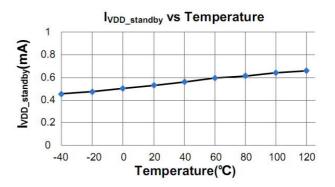

## ■ 参数特性曲线

## ■ 功能描述

FS6224 是一款高性能、多模式且采用断续模式 (DCM)工作的原边控制器。芯片内高精度的恒流、 恒压控制机制结合完备的保护功能,使其适用于小功 率离线式电源应用中。

### ● 系统启动

在芯片开始工作之前,FS6224 仅消耗典型值为2uA的启动电流,超低启动电流可以帮助增加启动电阻阻值以达到降低由直流母线流经启动电阻的电流和待机功耗的目的。当 VDD 电压超过开启电压(典型值 16.3V), FS6224 开始工作并且芯片工作电流上升到 1mA(典型值)。之后 VDD 电容持续为芯片供电直至输出电压建立后由辅助绕组为芯片供电。

图 1

一旦芯片进入到超低频工作模式中,FS6224的工作电流便进一步降低到 0.5mA(典型值),以帮助降低系统待机功耗。

### ● 原边恒压控制(PSR-CVM)

$$V_{FB} = (V_0 + V_F) \times \frac{Na}{Ns} \times \frac{R1}{R1 + R2}$$

其中: Vo 和 VF 分别为输出电压和副边续流二极管导通电压; R1 和 R2 为由辅助绕组连接到 FB 管脚的分压电阻; Ns 和 Na 分别为副边绕组和辅助绕组匝数。

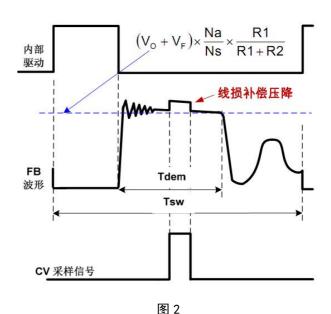

在原边控制技术中,当原边向副边传输能量时,通过采样与副边绕组耦合的辅助绕组电压,得到输出电压反馈信号。图 2 展示了 FS6224 内部 CV 电压采样时序以及关键波形。随着副边电流的续流到零,存在着副边续流二极管导通压降 VF 的降低过程。为了通过辅助绕组获得高精确的输出电压信息,芯片内的恒压采样模块屏蔽了由于漏感导致的关断时刻的电压振荡。当恒压采样过程结束时,内部的采样保持模块记录下反馈误差并通过内部的误差运算放大器将其放大。原边恒压控制模块利用误差运算放大器的输出实现高精度的恒压输出。芯片内部恒压输出基准为高精度的 2V。

在恒压采样过程中,FS6224 内部有一可变电流源从FB管脚流出用作线损补偿,如图 2 所示,由此将在FB波形上产生一电压阶梯。图 2 也展示了消磁过程中FB电压平台的量化关系:

当系统进入到过载模式后,随着输出电压的降低 FB 电压将降低至内部输出电压基准 2V 以下,之后 芯片也将自动进入到恒流输出模式中。

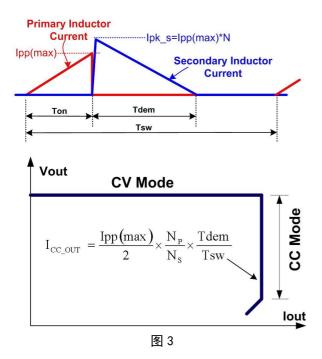

#### ● 原边恒流控制 (PSR-CCM)

芯片利用 FB 管脚电压和 CS 管脚电压的时序关系,可以实现高精度的恒流输出控制。如图 3 所示,在

恒压输出模式当系统输出功率增加且接近恒流输出 控制点时,原边电感电流达到其最大值。

如图 3 以上所示,原边电感电流、变压器匝比、副边消磁时间(Tdem)和开关周期时间(Tsw)决定了副边平均输出电流。如果忽略漏感的影响,副边平均输出电流的公式在图 3 已示。当输出电流达到原边恒流控制模块的输出基准时,芯片将进入调频工作模式中,无论输出电压低于恒压输出基准或者具体如何,只要 VDD 电压不低于其关断电压芯片将持续工作。

在 FS6224 内部,在恒流输出模式中消磁时间Tdem 与开关周期 Tsw 的比例被严格控制为 1/2。所以实际平均输出电流可以表示为:

$$I_{CC\_OUT}(mA) \cong \frac{1}{4} \times N \times \frac{500mV}{Rcs(\Omega)}$$

#### 其中:

N----变压器原边绕组与副边绕组匝数之比。

Rcs---连接于功率 MOSFET 源极与 GND 之间的采样 电阻。

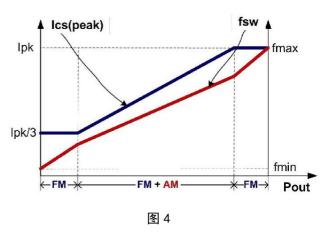

#### ● 多模式恒压控制

如图 4 所示,为了满足严苛的平均效率和待机功耗要求,FS6224 采用了调幅控制(AM)和调频控制(FM)

结合的多模式控制技术。

接近满载输出时,系统工作在调频工作模式中;在 轻重载条件下,系统工作在调频工作和调幅工作模 式中;当系统接近空载输出时,系统工作在调频模 式中以降低待机功耗。利用此种控制技术,系统可 以获得低于 70mW 的待机功耗。

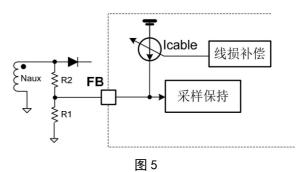

#### ● 恒压模式可调线损补偿(CDC)

在手机充电器的应用中,电池与充电器之间一般会通过一定长度的电缆相连,由此也将导致输送到电池端的电压产生一定的电压降。如图 5 所示,在FS6224 内部存在由线损补偿模块控制的可调式电流源流出到与 FB 管脚相连的分压电阻上并产生一定的电压偏置信号。此电流正比于开关周期,而反比与输出功率,所以在电缆上的电压降可以被补偿掉。随着负载功率的降低,在 FB 上的偏置电压将被提高。通过调节分压电阻 R1 和 R2 的阻值可以调节实际补偿量的大小。最大的线损补电压与输出电压基准的比例为:

$$\frac{\Delta V(cable)}{Vout} \approx \frac{Icable\_max \times (R1//R2)}{V_{FB\ REF}} \times 100\%$$

比如: R1=3KΩ、R2=18KΩ, 则:

$$\frac{\Delta V(cable)}{Vout} = \frac{60uA \times (3K//18K)}{2V} \times 100\% = 7.7\%$$

### ● 优化的动态响应

FS6224 优化设计的动态响应性能,可满足 USB 充电器的要求。

### ● 芯片过温保护 (OTP)

当芯片的温度超过 165°C时, 芯片就会停止开关动作, 此时只有芯片温度下降到 135°C以下, 芯片才能恢复开关动作。

#### ● 无异音工作

如上所述,在恒压输出模式中芯片采用了调频控制与 调幅控制结合的多模式控制技术,同时在 CS 管脚有 一电流源流出调节 CS 电压信号。利用以上技术,FS6224 可实现由满载到空载全程无异音工作。

#### ● 短路保护 (SLP)

在 FS6224 内部,输出电压通过 FB 管脚实时采样并与欠压保护阈值(典型值 0.7V)相比。 当采样到的 FB 电压低于 0.7V 且持续时间超过 10ms 时,芯片将进入到短路保护模式并自动重启。

### ● VDD 过压保护(0VP)和钳位

当 VDD 电压超过 30V(典型值)时,芯片立即停止开关动作。之后将导致 VDD 下降,当 VDD 电压低于关断电压 VDD\_0FF (典型值 9V)时,系统将重新启动。在芯片内部设计有 34.5V(典型值)的钳位电路以防止芯片受损。

### ● 管脚悬空保护

FS6224 内部设计有管脚悬空保护电路防止系统 受损。

#### ● 软驱动

FS6224 设计的软驱动功能的驱动电路优化了统EMI性能。IC内部设计有 Gate 高电平 16V 箝位电路,以防止高 VDD 输入时 Gate 受损。

# ■ 封装尺寸

| 符号 | 尺寸 (毫米)  |                     | 尺寸 (英寸) |       |

|----|----------|---------------------|---------|-------|

|    | 最小       | 最大                  | 最小      | 最大    |

| Α  | 1.350    | 1.750               | 0.053   | 0.069 |

| A1 | 0.100    | 0.250               | 0.004   | 0.010 |

| A2 | 1.350    | 1.550               | 0.053   | 0.061 |

| b  | 0.330    | 0.510               | 0.013   | 0.020 |

| С  | 0.170    | 0.250               | 0.006   | 0.010 |

| D  | 4.700    | 5.100               | 0.185   | 0.200 |

| E  | 3.800    | 4.000               | 0.150   | 0.157 |

| E1 | 5.800    | 6.200               | 0.228   | 0.244 |

| е  | 1.270 (中 | 70 (中心到中心) 0.050 (中 |         | 心到中心) |

| L  | 0.400    | 1.270               | 0.016   | 0.050 |

| θ  | 0°       | 8°                  | 0°      | 8°    |